# A Perspective on Manufacturing 2.5/3D

Bob Patti, CTO rpatti@tezzaron.com

# 2.5 and 3D Opportunities & Goals

- Choices:

- Interposers

- Organic

- Silicon

- Glass

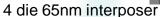

- Chip stacking

- Wafer to wafer

- Die to wafer

- What do we want from doing this?

- Performance

- Power

- Size

- Cost ?

- Near Term -- Only from the system

3D is Coming of Age

#### Samsung

Wide Bus DRAM

Micron

Wide Bus DRAM Intel

CPU + memory

OKI

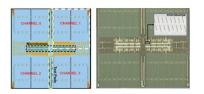

**CMOS Sensor**

Xilinx

#### Raytheon/Ziptronix

**PIN Detector Device**

#### **IBM**

RF Silicon Circuit Board / TSV Logic & Analog

#### Toshiba 3D NAND

Samsung

22 layer 3D NAND

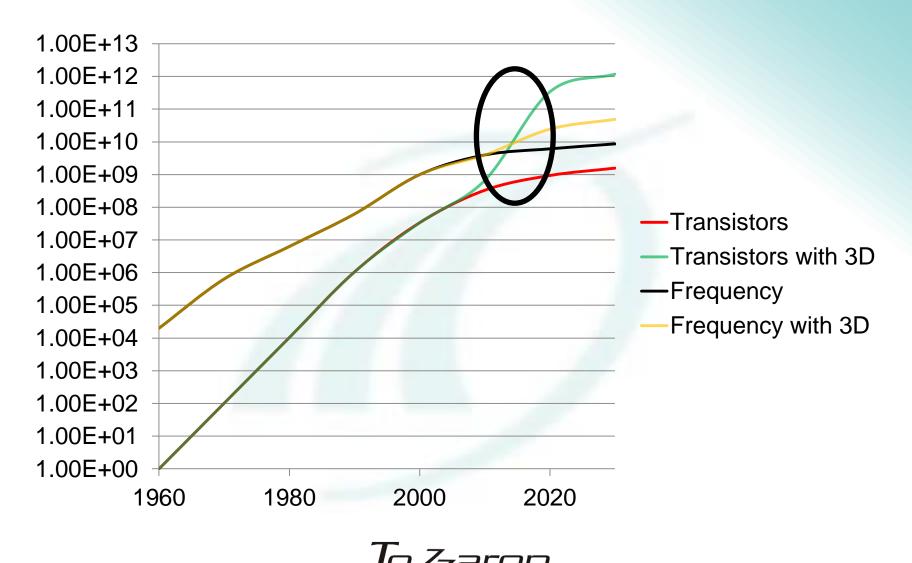

### The Effect of 2.5/3D on Devices

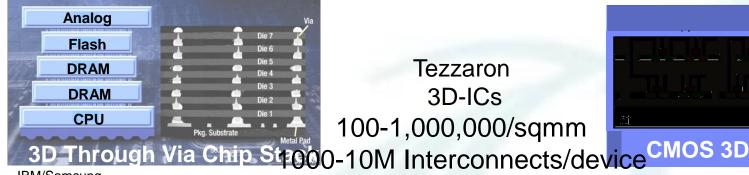

# Span of 3D Integration

#### **Rich and Varied Technologies**

Packaging

Wafer Fab

Tezzaron 3D-ICs 100-1,000,000/sqmm

IBM/Samsung

**IBM**

### 1s/sqmm

Peripheral I/O

- Flash, DRAM

- **CMOS Sensors**

100,000,000s/sqmm Transistor to Transistor

Ultimate goal

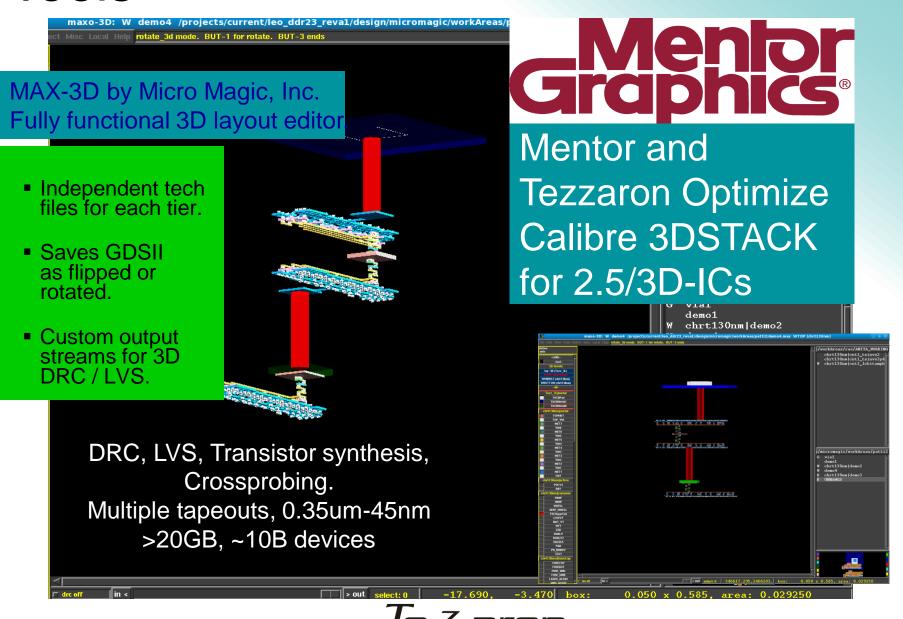

### **Technical Advances**

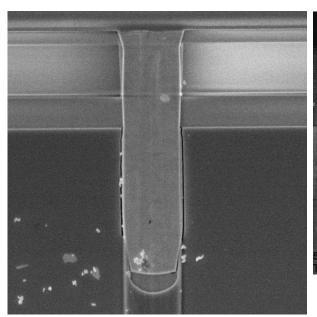

- TSV quality

- Metrology

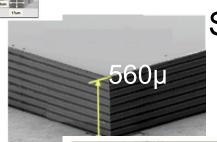

- Thinning control

- TSV end point detection

- CAE tools

- 3D DRC/LVS

- Simulation of 3D devices

- Bond quality

- Designers have some handle on what can be done

## **Industry Advances**

- There is an ecosystem

- It is still young but it is in exponential growth mode

- Vendors are 3D aware!

- TSV specific process hardware

- 2.5D and 3D specific CAD

- It is not if but when

Tezzaron 3D Devices

SEMICONDUCTOR

# **High Performance 3D Memory**

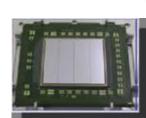

#### Octopus – Proof of Concept

- 1-4Gb

- 16 Ports x 128bits (each way)

- @1GHz

- CWL=0 CRL=2 SDR format

- 5ns closed page access to first data (aligned)

- 12ns full cycle memory time

- >2Tb/s data transfer rate

- Max clk=1.6GHz

- Internally ECC protected, Dynamic self-repair, Post attach repair

- 115C die full function operating temperature

#### DiRAM4™

- 4-64Gb

- 64-256 Ports x 64bits (each way)

- @1GHz

- 5-7ns closed page access to first data (aligned)

- 12ns full cycle memory time

- >16Tb/s data transfer rate

- 4096 banks

- 2+2pJ/bit

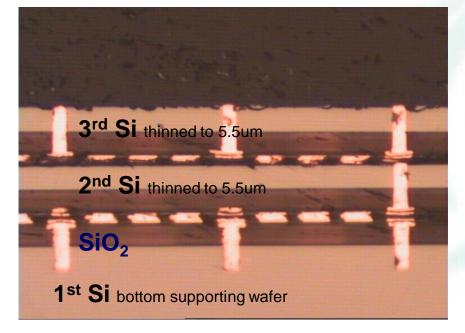

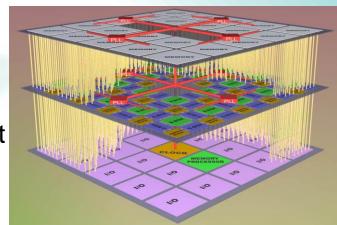

# DiRAM4 "Dis-Integrated" Memory

connections per lay per

**DRAM layers** 4xnm node

Controller layer contains: senseamps, CAMs, row/column decodes and test engines. 40nm node

Better yielding than 2D equivalent!

die I/O layer contains: I/O, interface logic

2 million vertical

and R&R control CPU. 65nm node

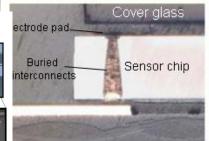

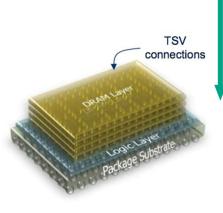

#### Capillar underfill C2W Cu2Cu bond 2.5/3D in Combination TSI TSV H:R CPU(2 Gbps serdes+2xDDR2 channel to 3DMem+2xDDR2 channel to PCB) IME A-Star / Tezzaron Collaboration 150um pitch IME A-Star / Tezzaron Collaboration μBumps Die to Wafer Cu Thermal Diffusion Bond C4 Bumps 3 Layer 3D Memory 2 Layer Processor FPGA (4Xnm) level#4 level#3 level#2 **Active Silicon Circuit Board Organic Substrate** level#1 level#0 **Solder Bumps**

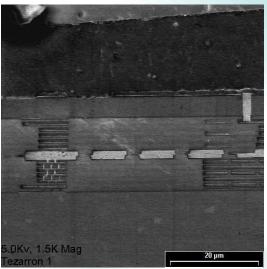

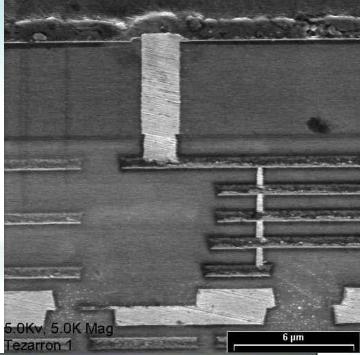

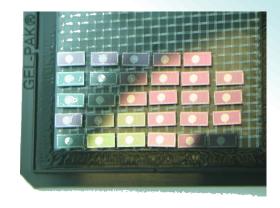

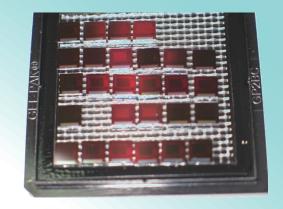

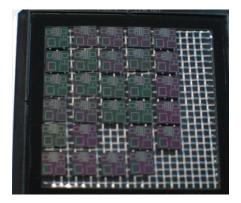

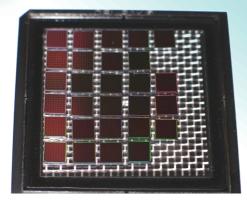

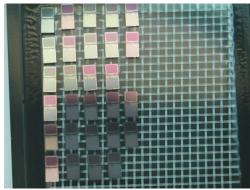

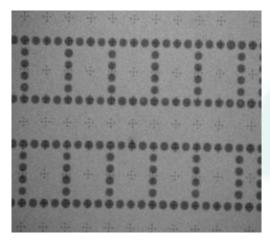

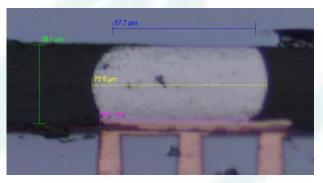

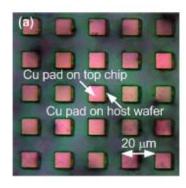

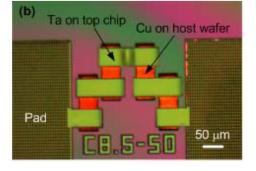

#### **Tezzaron Dummy Chip C2C Assembly**

Memory die

C2C sample

X-ray inspection indicated no significant solder voids

X-section of good micro bump

CSCAN showed no underfill voids (UF: Namics 8443-14)

### WHAT IS IMPORTANT?

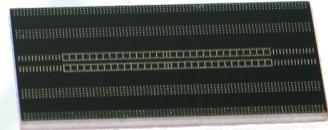

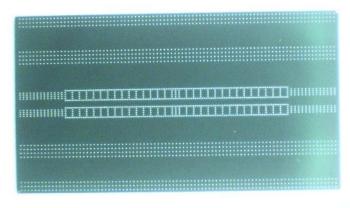

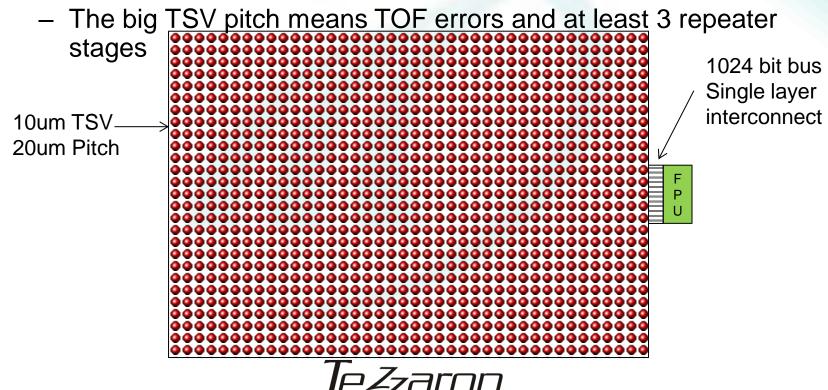

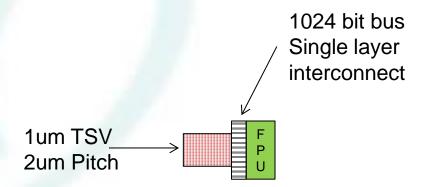

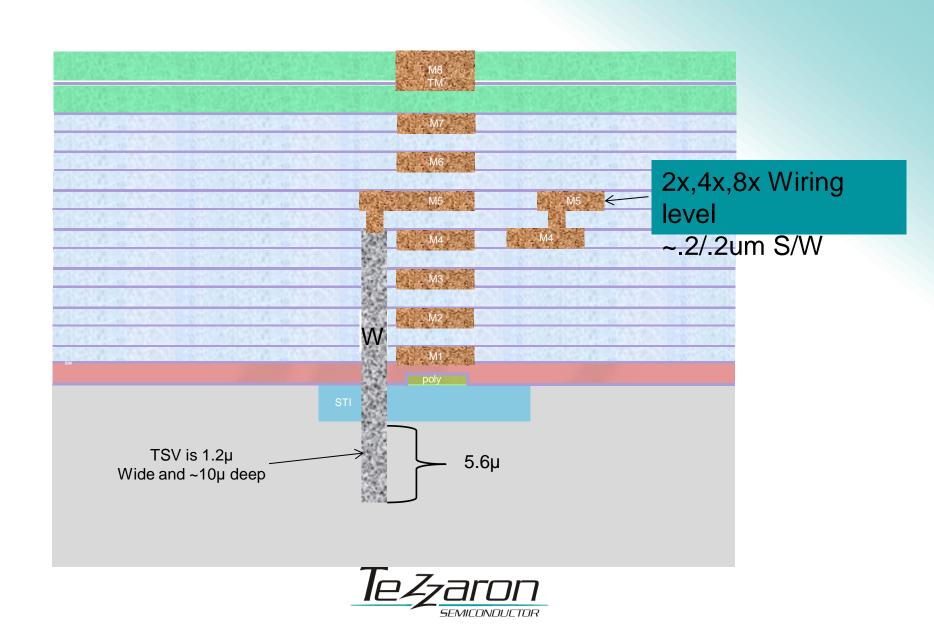

### TSV Pitch ≠ Area ÷ Number of TSVs

#### TSV pitch issue example

- 1024 bit busses require a lot of space with larger TSVs

- They connect to the heart and most dense area of processing elements

- The 45nm bus pitch is ~100nm; TSV pitch is >100x greater

### TSV Pitch ≠ Area ÷ Number of TSVs

#### TSV pitch issue example

- 1024 bit busses require a lot of space with larger TSVs

- They connect to the heart and most dense area of processing elements

- The 45nm bus pitch is ~100nm; TSV pitch is >100x greater

- The big TSV pitch means TOF errors and at least 3 repeater stages

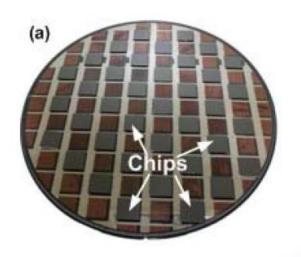

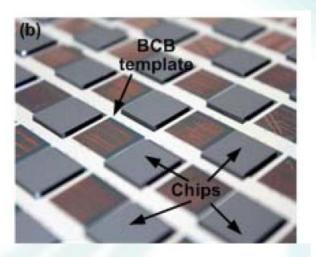

### Die to Wafer – 2.5D

RPI/Dr. James Lu

- •KGD

- Multilayer capability

- •Incremental risk buy down

- Extends SOC concepts

#### **Tools**

### What Has Tezzaron Learned?

- Systems require multiple solutions

- SIP is the future of SOC

- Logic, Memory, Analog, MEMS, Photonics, Cooling

- InP, GaAs, SiGe, GaN, CNT

- To practice 2.5 and 3D you need multiple technologies

- Cu-Cu

- DBI

- 150C bonding

- Oxide, IM, gold

- Via middle

- Via last

- Cu TSV

- W TSV

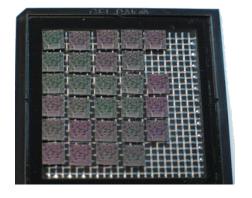

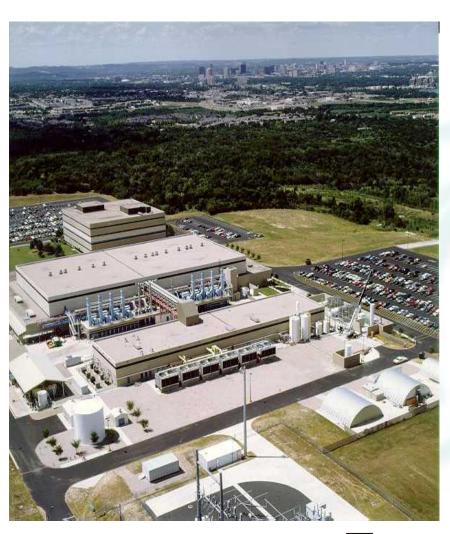

#### Tezzaron/Novati

- "Volume" 2.5D and 3D Manufacturing in 2013

- Interposers

- Future interposers with

- High K Caps

- Photonics

- Passives

- Power transistors

- Wholly owned Tezzaron subsidiary

- Cu-Cu, DBI<sup>®</sup>, Oxide, IM 3D assembly

# **Facility Overview**

#### **Capabilities**

- Over 150 production grade tools

- 68000 sq ft Class 10 clean room

- 24/7 operations & maintenance

- Manufacturing Execution Systems (MES)

- IP secure environments, robust quality systems

- ITAR registered

- Full-flow 200mm silicon processing, 300mm back-end (Copper/Low-k)

- Process library with > 25000 recipes

- Novel materials (ALD, PZT, III-V, CNT, etc)

- Copper & Aluminum BEOL

- Contact through 193nm lithography

- Silicon, SOI and Transparent MEMS substrates

- Electrical Characterization and Bench Test Lab

- Onsite analytical tools and labs: SIMS, SEM, TEM, Auger, VPD, ICP-MS, etc

- ISO 9001:2008 13485:2013

- TRUST 2013

# The Big Problems Left Are...

- Test

- 5k I/O going to 20k I/O going to 100k I/O

- When is the testing good enough?

- Biggest hidden cost

- The right processes

- HVM scaling

- The heavy CAD tools

- 3D aware synthesis, P&R

- We don't know what we don't know

# Ongoing: Work to be Done

#### **New Data Needs and Standards**

- Notch

- Orientation limitations

- Run out / street size / magnification

- Die location

- TCE matching / stress / warpage

- TCE zero match at what temperature?

- Materials

- Planarity

- Surface roughness

### **Decisions to Make**

#### 2.5D Alternatives

- Silicon Interposers

- 2-3um L/S/D

- Rs and Cs

- Active is the future

- Handling & handoff

- Organics

- 5-6 um

- Litho limits

- Material planarity limits

- Great cost structure

- TCE Challenges

- Large substrate

- Glass

- Large substrate

### THE ROAD AHEAD...

### **Near End-of-Line TSV Insertion**

### **Photonics for Short Haul**

14nm FF Chip

- 16x100G Optical Transceivers

- 8 Optical I/O per Couplers

- Four optical power supplies

Photonic Interposer with TSVs

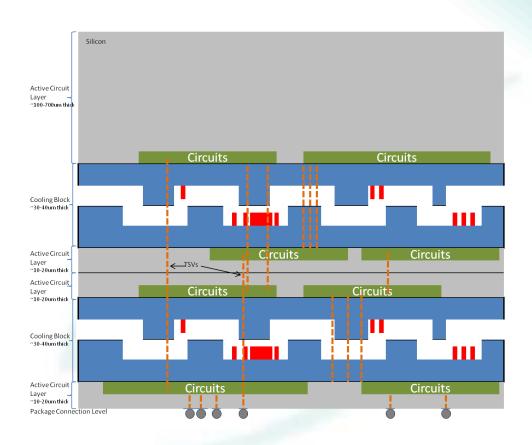

# Integrating Fluidics into 3D: Liquid Cooling

It's a MEMS, 2.5D SOC/SIP future...

# "5.5D" Systems

- SIP/SSIP

- Power Conversion

- Cooling

- Photonics

- Optimization

- Extending to power

- Mixed PCB/IC Metaphor

# Summary

- Industry has the momentum

- Generating tools and technology

- Problems are now deemed solvable

- 3D is proving value

- There is production and it is expanding

- Lingering questions about who does what

- Foundry to OST interface

- Test and HVM processes are the growth opportunities

Sensors

Computing MEMS

Communications